忧郁的大能猫

忧郁的大能猫

好奇的探索者,理性的思考者,踏实的行动者。

blog/A-IT/00-CS基础/00-硬件/说透芯片-极客时间

Table of Contents:

开篇词 | 为什么你一定要了解芯片行业

01 | 核心概念:从晶体管到集成电路到摩尔定律

芯片和半导体是同一个事物的两个名字,芯片是半导体产业的产品,半导体是用来做芯片的材料。这个行业,通俗一点,就叫芯片行业,学术一点就叫半导体行业,相当于土豆和马铃薯的区别。

半导体产业是电子产业的一个分支。如果你想入行,可以读电子工程系的微电子专业,或者集成电路专业,前者毕业可以从事芯片制造,后者毕业可以从事芯片设计。

你听到我说 28nm、20nm、14nm、10nm、7nm、5nm 这组数字的时候,你心中或许有疑问,为什么选这些数字?有什么规律么?你问到重点了。基本上这是个相邻两个数字差 0.7 倍的数字序列,你看,10nmx0.7=7nm,7nmx0.7≈5nm,都是这样的规律。如果把晶体管的特征尺寸理解成正方形的边长,边长缩小 0.7 倍,0.7x0.7=0.49,那么一个正方形的面积就相当于小了一半。

这种相差 0.7 倍的数字序列,想表达的意思就是,在 5nm 制造工艺下,晶体管的体积应该是前一代 7nm 工艺的一半,换另一个数据来说就是晶体管密度可以高一倍

- 电子管开创了电子时代,人类的第一台计算机是拿电子管搭建的。半导体晶体管,复刻了电子管的所有功能,但是点开了“可以持续缩小体积”的科技树,即集成电路。

- 晶体管,集成电路,这是半导体行业的两个基础发明,有两项诺贝尔奖加持。

- 摩尔定律的背后推手是晶体管尺寸的不断缩小,因此单位面积可以集成的晶体管数目在不断增多。摩尔定律对电子行业的影响就是微处理器的性能每隔 2 年提高一倍,或价格下降一半,再向设备侧延展,就是相同价格所买的电脑,性能每隔 2 年增加一倍。

02 | 从一部iPhone手机看芯片的分类

芯片和集成电路是什么关系?

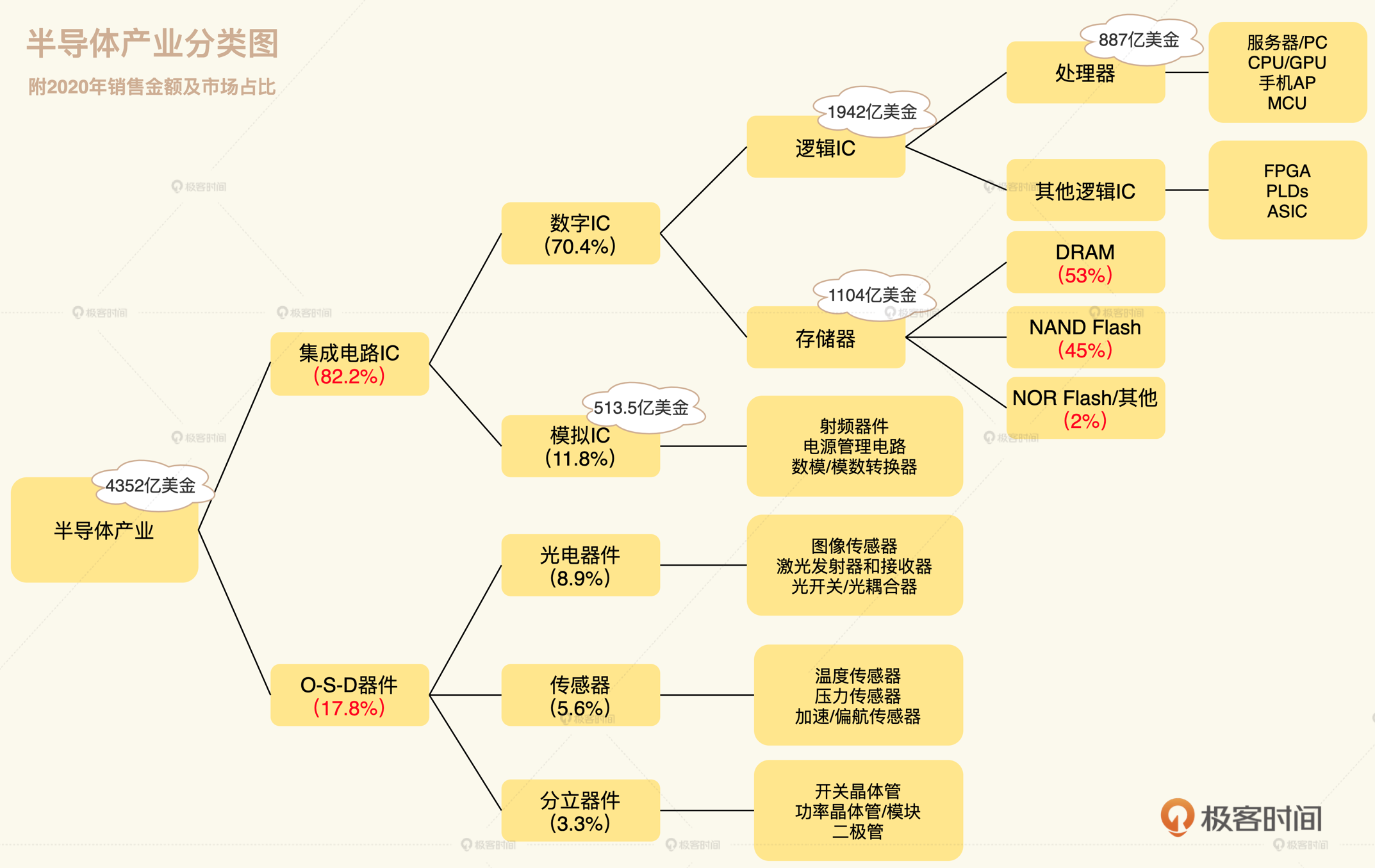

芯片肯定不全是集成电路。芯片里面,大约只有 80% 属于集成电路,其余的都是光电器件、传感器和分立器件,行业内把这些器件称为 O-S-D(Optoelectronic, Sensor, Discrete)。

集成电路你已经学过了,它是由大量晶体管组成的

- 在半导体行业中,超过 80% 的产品是集成电路芯片,因此我们在日常中常把芯片、半导体、集成电路三者混用。但其实,集成电路之外,半导体产品还有光电器件、传感器和分立器件,行业内称为 O-S-D;

- 集成电路芯片主要分为数字 IC 和模拟 IC,数字 IC 强调运算速度,模拟 IC 强调高信噪比、低失真、低耗电和高稳定性,生命周期更长;论销售额,数字芯片有绝对优势,但是如果论出货量,模拟芯片量大过数字芯片。

- 数字 IC 中主要就是 CPU 处理器和存储器。CPU 是重中之重,行业明珠的地位。无论是 Intel,还是苹果,都是靠 CPU 站在行业第一的位置的。

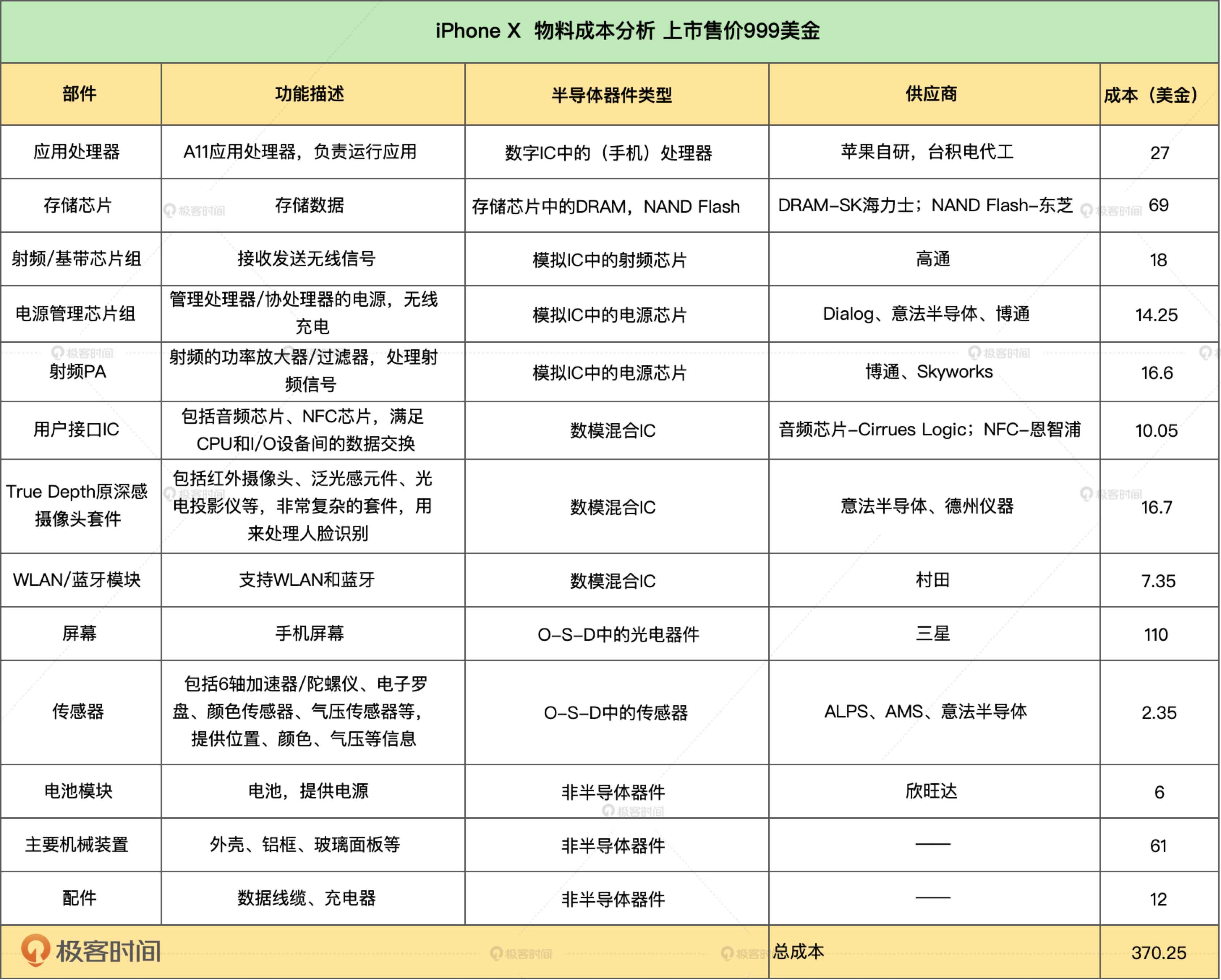

- 一部 iPhone 手机,基本上用到了半导体产品的全部种类。一部小小的手机,是整个行业的缩影。选车要看发动机,我希望你在选择下一部手机的时候,也能看看它的芯片。

03 | 芯片设计:一颗芯片到底是如何诞生的(上)

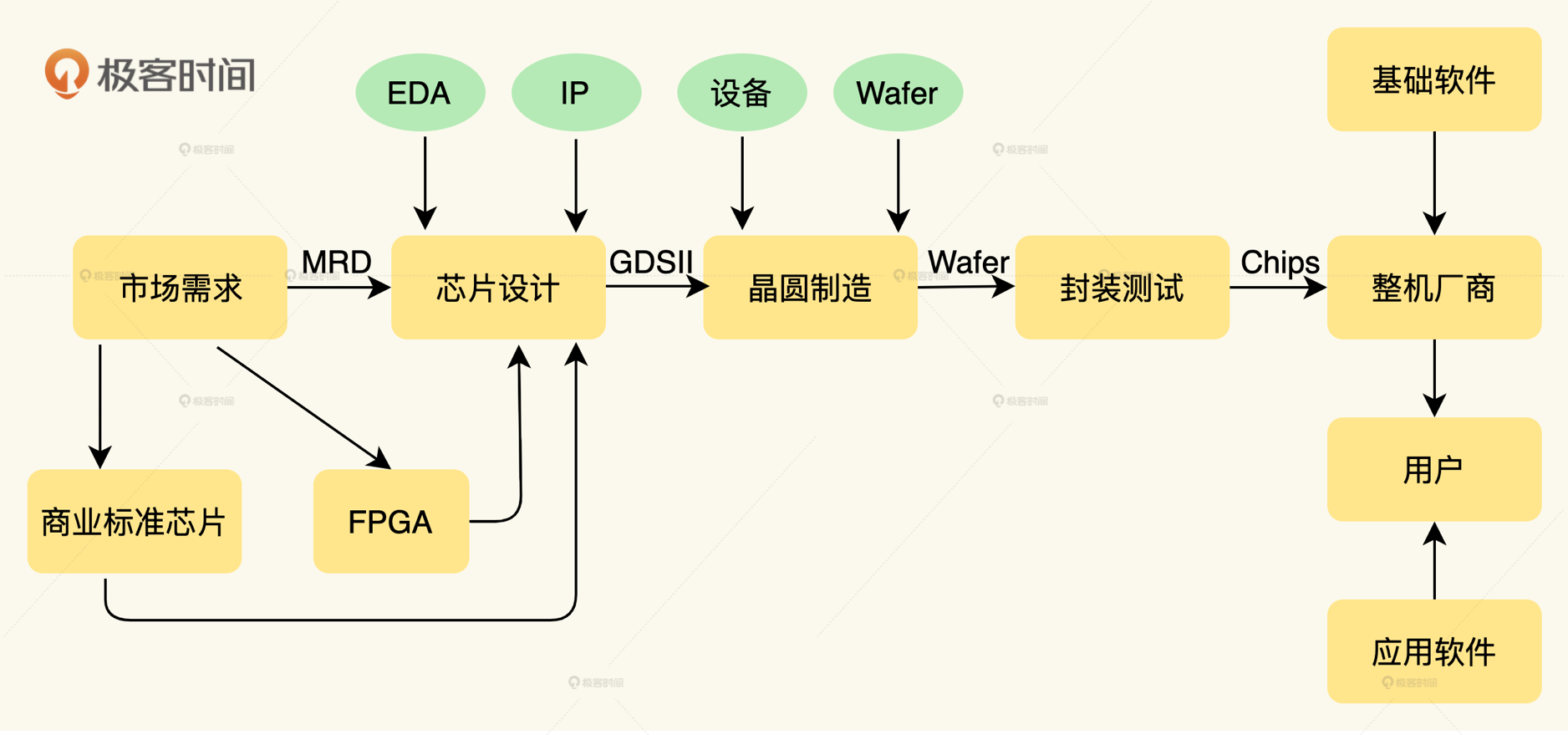

你一定要记住这张图,基本上它对所有的电子设备,从指纹密码锁,到手机、PC、服务器,甚至超级计算机,都是适用的。

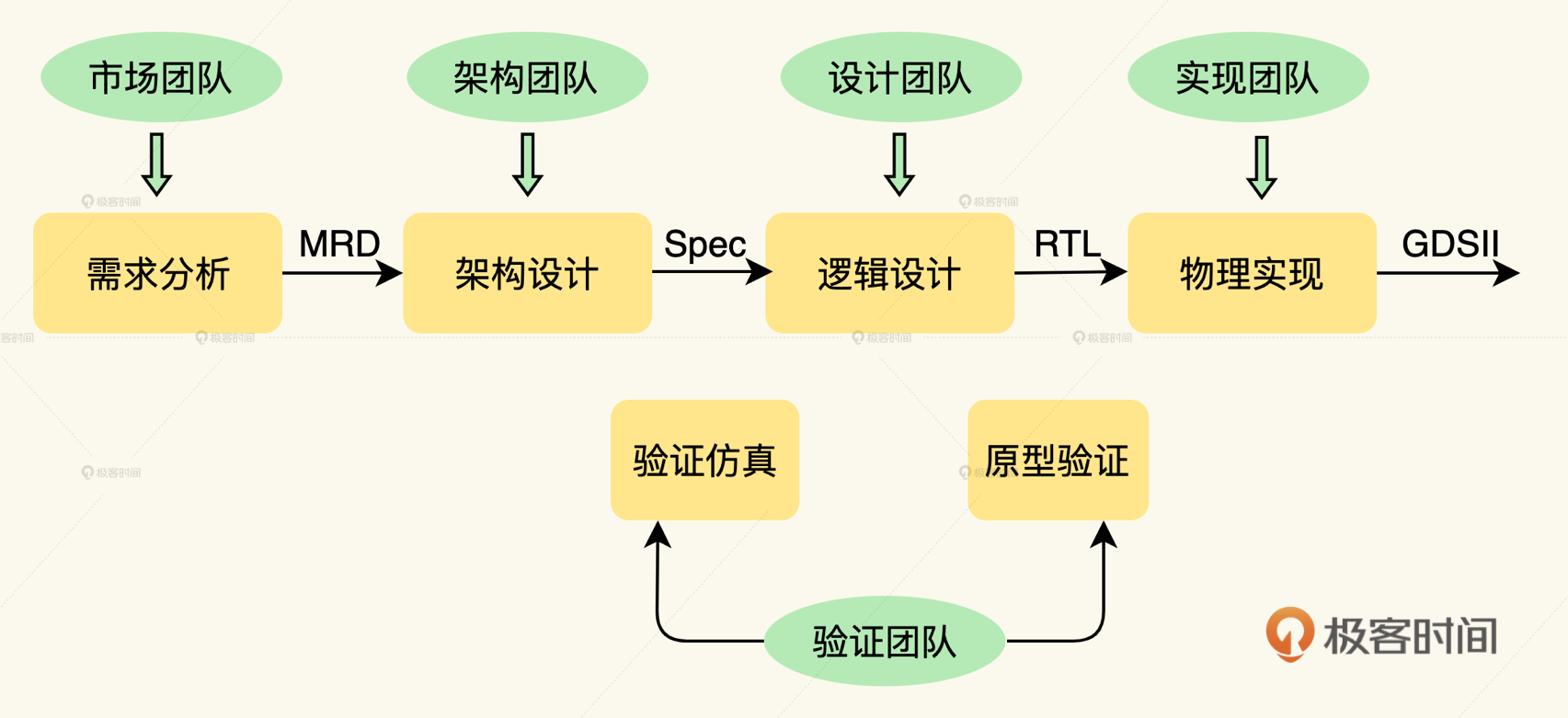

如果只看芯片设计,它主要包含需求分析、架构设计、逻辑设计、物理实现和验证等几个部分。

如果说芯片项目和其他产品项目有什么不同,那就是芯片项目是人类历史上最细微也是最宏大的工程,研发投入大,项目收益高,试错成本极高。

需求分析

在芯片公司发现市场需求之后,通常会进行市场调查,总结出一个通用的市场需求清单出来。一般这个需求清单,会包括主要应用场景分析、软件栈、竞争分析、性能与定位、需求量与投资回报比分析、行规与标准,主要配套芯片的市场供应情况预测等多项内容。最终形成的就是一份市场需求文档。

架构设计

一个项目是否有商业价值,主要看需求分析。而一个芯片是否做得好,80% 是由架构设计决定的。

在拿到需求分析文档后,高层设计人员,往往是以架构师为主的团队,需要开会对产品需求逐条进行可行性分析,并在此基础上确定基本架构和模块分解,最终设计出一个系统架构。

在基本架构确定之后,芯片的大目标,就是对 Power 功耗、 Performance 性能、Area 面积,也就是业内常提到的 PPA 衡量标准,要有明确的规划,这一般也就确定了要选择的制造工厂和工艺制程。

到架构设计这一步,最终输出的就是一份产品规格书和高层架构设计文档。这是一个将市场需求,翻译为可实现的芯片架构过程。

有了一个可行的芯片设计方案和芯片原型模型之后,架构团队就可以把文档和芯片模型移交给设计团队,开始逻辑设计。

逻辑设计

前端设计与验证

前端设计(逻辑设计)一般用硬件描述语言,例如 Verilog,将架构师的设计用编码实现。其实硬件描述语言,看起来跟 C 语言颇为类似,不过写 C 语言的人,心里想着“hello world”,写 Verilog HDL 的人,心里想着电路图。

跟其它的软件项目一样,在设计的同时,验证也要并行进行。验证是芯片设计中最为耗时耗力的工序,ARM 的技术白皮书有统计,一般一个项目的 40% 资源是用在验证阶段的。

逻辑综合

设计验证完成之后,还有一个步骤,叫逻辑综合 (Logic Synthesis),就是用 EDA 工具把寄存器传输级设计 RTL 描述变网表(Netlist),非常类似于编译器把 C 语言翻译成机器语言的过程。从这一步开始,芯片的设计就和具体的晶圆代工厂和具体工艺绑定在一起,设计开始具有物理特征了。

网表表示的电路如下图,它其实就是描述电路元件相互之间的连接关系。

DFT(可测试性设计)

除了以上两步,前端设计还有一个步骤就是 DFT(Design For Test)。所谓 DFT,就是预先规划并插入各种用于芯片测试的逻辑电路。芯片制造后期,在封测阶段中,很多测试需要依赖 DFT 的设计。

完成以上工作后,前端设计团队就可以将生成的网表交给后端实现团队,开始物理设计了。当然这个过程不是一蹴而就的,前端设计工程师往往要多次,不同层次的反复综合、验证,各种设计规则检查,既要确保设计的正确性,又要保证设计的布局布线可行且优化。

整个逻辑设计阶段,你可以这样理解:架构师写在文档上的指标与功能,是需要设计团队通过一行行的代码实现出来的。

物理实现

在前端设计结束后,后端也就是物理实现需要完成布局布线,这个时候,需要把网表转换成制造工厂可以看懂的文件,也就是转化为制造工厂可以用来制造光罩的图形文件。

后端设计的主要步骤可以总结为:布局规划 Floorplan→布局 Placement→时钟树综合 CTS→布线 Routing →物理验证。

布局规划就是在总体上确定各种电路的摆放位置,它是后端实现中最为重要的一个环节。芯片的面积、时序收敛、稳定性、走线难易,基本上都是受布局规划的影响。

规划之后,在指定区域摆放元器件,就是布局,而把各个元器件连接起来,就是布线。一颗芯片的树状的时钟信号线路非常重要,往往需要单独布线,因此还有一个专门的名称:时钟树综合。最后,要做验证。

我说得简单,其实这就是在指尖上建高楼,在小小的芯片上放置上百亿个晶体管,纳米级的单位,幸而有 EDA 工具辅助,这不是人力所及的工程。

一颗芯片做得好不好,在决策阶段取决于市场需求理解的是否深刻,在逻辑设计阶段取决于工程师的能力强不强,而在物理实现阶段基本取决于 EDA 工具玩得好不好。

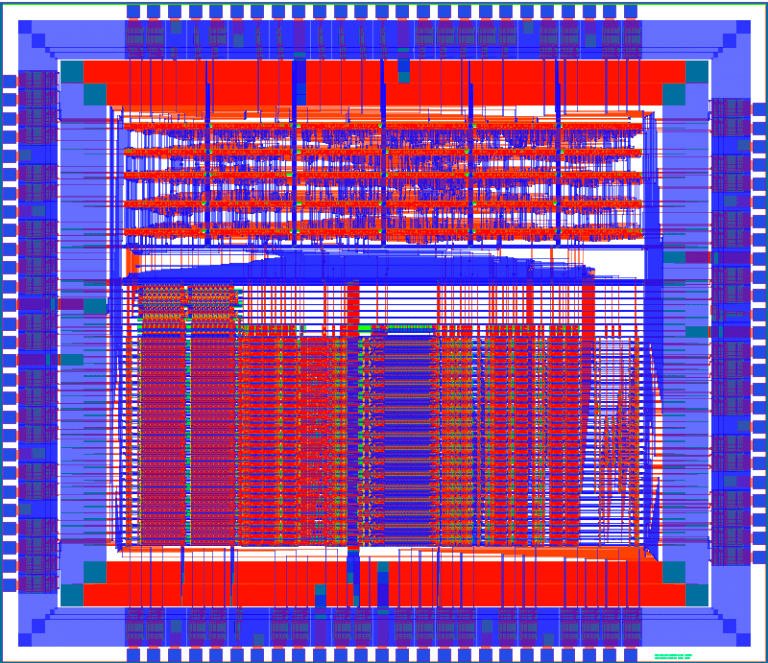

物理设计完成之后就形成了下图展示的电路图。图中可以看到蓝、红等不同颜色,每种颜色就代表着一张光罩。这个时候的芯片设计就可以以 GDSII 的文件格式从设计公司移交给芯片代工厂了。自此,设计完成,制造流程开始。

04 | 芯片制造:一颗芯片到底是如何诞生的(下)

对于整个芯片的制造过程,我给你分了三个步骤让你理解,包括上游的晶圆材料准备,中游的晶圆加工,和下游的封装与测试。

- 半导体行业的两个重要增值的过程是:晶圆加工和芯片设计。最先进工艺的晶圆制造,价值不菲,是制造业的顶级工艺。

- 晶圆的加工过程,就是在晶圆上制造集成电路的过程。更准确的说,是在晶圆构造海量晶体管的过程。其中光刻环节最为重要。

- 晶圆加工完成之后,还要经过切割,测试,封装为芯片。封装技术,已经成为和架构、工艺并行的第三大技术。

- 台积电的出现,促使了半导体公司由一包到底的 IDM 模式,向代工模式转换。半导体行业是全球化分工最早最彻底的行业之一。

05 | Intel的发展史就是一部芯片行业的创新史(上)

- 看 Intel 的历史,就是在看半导体行业竞争的关键点。我给你总结了 Intel 持续保持领先的几个关键因素,让你更好地理解在一个行业中,竞争与发展的逻辑。

- Intel 在发展的第一阶段,虽然从存储芯片的市场落败,但是很好地抓住了 PC 市场,这个半导体行业的第一次机会,确立了以 CPU 为核心的产品路线,并确立了行业第一的地位。

- Intel 在公司的发展初期,选择对了产品(半导体最大的品类,存储器),而且技术创新领先(各种世界第一),也结合了自己的强项(工厂生产)。从一个初创公司角度,无论在技术,商业上都没大问题,但是输给了强大的竞争对手:日本政府。

- 在半导体行业,Intel 最先意识到指令集向后兼容性的价值,也因此,它战胜了 Zilog 的 Z80。而指令集的实质是软硬件之间的标准,Intel 掌握了这个标准,并且后来在微软的帮助下,把 x86 做成 IT 业的事实标准,Intel 才拥有今天的江湖地位。

06 | Intel的发展史就是一部芯片行业的创新史(下)

看 Intel 的历史,就是在看半导体行业竞争的关键点。我给你总结了 Intel 持续保持领先的几个关键因素,让你更好地理解在一个行业中,竞争与发展的逻辑。

- Intel 的成功是摩尔定律的成功,是不断突破极限的产品开发的成功。

- 在半导体行业,除了设计和生产两个方面,Intel 最先意识到指令集向后兼容性的价值,也因此,它战胜了 Zilog 的 Z80,也才有了 Wintel 联盟形成的强大的 x86 生态。

- 赢得 PC 市场,Intel 得益于 IBM PC 与兼容机全开放式的思路,Intel 与 AMD 这对兄弟相杀相爱多年,在服务器市场,他们是同盟军,联手绞杀一众古典 RISC 厂商。在 PC 市场,他们又是你死我活的竞争对手。

- Intel 的 Tick-Tock 策略,曾经是行业标准的摩尔时钟,在 Intel 的 Tick-Tock 失速之后,其实是苹果默默接手,推动行业继续按照摩尔定律发展。因此是否能重启 Tick-Tock 策略,才是 Intel 的生死关键。